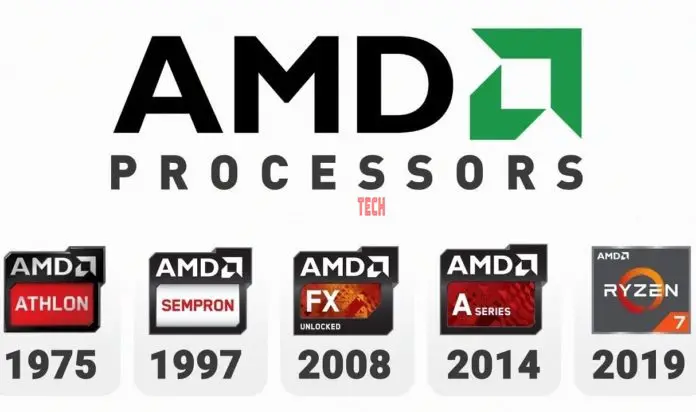

As discussed in my previous article about AMD History, its beginning before the making of microprocessor.

In this article I will be telling you what phases went by after AMD was born.

It was in 1969 just a year after Intel, Amd was born. Jerry sanders the worldwide sales manager at Fairchild Semiconductor laid the foundation of AMD with his team of seven.

In the September of 1969, AMD moved from its temporary location in Santa Clara to Sunnyvale, California. Initially AMD started to supply microchips, designed by Fairchild and National semiconductor. At first AMD focused on producing logic chips, where the company guaranteed quality control to United States Standard. Many computer manufacturers, telecommunication industry and instrument manufactures wanted reliability in microchips.

In the month of November 1969, AMD manufactured its first product, the Am9300. It was a 4-bit MSI shift register and started selling in 1970. In the same year AMD produced its first proprietary product, the Am2501 logic counter, which became very successful.

AMD bestselling product in 1971 was the Am2505, the fastest multiplier. In the same year AMD entered into the RAM market with the Am3101 (a 64-bit bipolar RAM).

In 1972 AMD went public, becoming a second source of the Intel MOS/LSI circuits with its products such as Am14/1506 and Am14/1507.

AM9080 and AM2900

By 1975 AMD had over 212 products which were being produced by the company. By the 212 products 49 were proprietary like the Am9102, while three low power schottky MSI circuits.

- Am25LS07

- Am25lS08

- Am25LS09

In the same year AMD entered into the microprocessor market with a reverse engineered clone of the Intel processor Intel 8080, called Am9080. It also created the AM2900 which was not a processor rather a series of component to build a 4-bit modular processor. Soon in 1976 AMD Was granted a copyright license to microcode in its processor by Intel.

In 1977 AMD entered into a joint venture with Siemens, where Siemens bought 20 percent of AMD share, thereby giving AMD a cash flow to increase its product lines. AMC (Advanced micro Computers) was established in Silicon Valley and Germany. After they parted ways AMD bought Siemens’ stake in the US division in 1979.

Throughout the 1980s AMD produced a line of 32-bit RISC processor called the AM2900 series. It was designed using a variety of Berkeley RISE architecture. Eventually it discontinued it to focus on the x86 processor.

In the mid of 1980 AMD had some success with the AMD 7910 and AMD 7911 “World chip”.

The Technology Exchange Agreement with Intel

This story starts with International Business Machines, the IBM, which had a share of 62 percent in the mainframe computer.

IBM entered the minicomputer market lately, as a result many new rivals such as Digital Equipment Cooperation the DEC and others earned billions. This time IBM did not wanted to repeat the mistake with personal computers.

In the late 1970s this market was hugely dominated by

- Commodore PET

- Atari 8-bit family

- Apple II series

- Tandy Corporation’s TRS-80, And many others.

A single IBM computer in 1960 would cost about $1million, whereas some successful company revenue would be $12million. In1980 the least expensive IBM computer would cost $13500 and was only sold through sales force.

In 1981 IBM created its PC and wanted Intel’s x86 processors, but under a condition that Intel will have to provide a second-source manufacturer for its patented x86 microprocessors.

After that Intl and AMD entered into a 10 year technology agreement, signed in October 1981 and formally executed in 1982. The same year AMD started manufacturing huge volume of Intel’s

- 8086

- 8088

- 80186

- 80188 processors

About Intel’s 8086 clone

| Release Date | 1982 |

| Architecture | 16-bit |

| Data Bus | 16-bit |

| Address Bus | 20-bit |

| Maximum Memory Support | 1 MB |

| L1 Cache | None |

| L2 Cache | None |

| Frequency | 4 – 10 MHz |

| FSB | 4 – 10 MHz |

| FPU | 8087 |

| SIMD | None |

| Fab | 3000 nm |

| Transistor Count | 29,000 |

| Power Consumption | N/A |

| Voltage | 5V |

| Die Area | 33 mm2 |

| Socket | 40 pins |

In 1983 AMD introduced INT.STD.1000 the highest manufacturing quality standard in the industry. In 1984 AMD established its clone of the Intel’s 80286 processor. In the same year it created the world’s first 512k EPROM.AMD second x86 processor was the Am286, which was a licensed clone of the Intel’s 80826. The advantage over Intel’s 80826 was that Am286 had higher clock speed. Intel capped with 12.5 MHz while pushed it a little further to 20MHz.

AMD AM286

| Release Date | 1983 |

| Architecture | 16-bit |

| Data Bus | 16-bit |

| Address Bus | 24-bit |

| Maximum Memory Support | 16 MB |

| L1 Cache | None |

| L2 Cache | None |

| Frequency | 8 – 20 MHz |

| FSB | 8 – 20 MHz |

| FPU | 80287 |

| SIMD | None |

| Fab | 1500 nm |

| Transistor Count | 134,000 |

| Power Consumption | N/A |

| Voltage | 5V |

| Die Area | 49 mm2 |

| Socket | 68 pins |

In 1985 AMD withdraw from the DRAM market and made headway to the CMOS market, which lagged even after having access to the bipolar chips. In the same tear Intel released its first 32-bit x86 processor design, the 80386. AMD then released its own version AM386. But that didn’t too long. Intel held it up in court. Intel claimed that its cross-licensing agreement permitted AMD to produce copies of only the 80286 and older processor designs, but AMD argued that the contract permitted it to create clones of the 80386 and future x86 derivatives, as well. After years of legal battles, the courts sided with AMD, and the company was able to release its AM386 in 1991.

Even though the AM386 was an 80386 clone, but it came up with 40 MHz while the Intel had 33 MHz . This gave AMD a performance advantage over Intel as it used the same socket and platform as the 80386, therefore the customers could upgrade their aging system. 1 million units of this processor were sold.

AMD AM386

| Release Date | 1991 |

| Architecture | 32-bit |

| Data Bus | 32-bit |

| Address Bus | 32-bit |

| Maximum Memory Support | 4 GB |

| L1 Cache | None |

| L2 Cache | None |

| Frequency | 12 – 40 MHz |

| FSB | 12 – 40 MHz |

| FPU | 80387 |

| SIMD | None |

| Fab | 1500 – 1000 nm |

| Transistor Count | 275,000 |

| Power Consumption | 2 W |

| Voltage | 5V |

| Die Area | 42 mm2 |

| Socket | 132 pins |

The Final Clone

The final clone AMD produced was the AM486 and released in 1944. While the AM386 was used for small computer manufacturers, but the AM486 became popular among large computer manufacturer. Like what we have seen with the AM386 processor, in similar when the Intel’s 80486 was capped at 100 MHz, AMD wend a little further as 120 MHZ with the AM486.

This was when the L1 cache was added to increase the performance, when compared to the AM386. It also moved the FPU to the same CPU package giving a slighter boost to the performance. Prior to this all FPU were sold as separate hardware units and connected to the CPU through the motherboard.

AMD AM486

| Date | 1993 |

| Architecture | 32-bit |

| Data Bus | 32-bit |

| Address Bus | 32-bit |

| Maximum Memory Support | 4 GB |

| L1 Cache | 8 – 16 KB |

| L2 Cache | None |

| Frequency | 16 – 120 MHz |

| FSB | 16 – 50 MHz |

| FPU | Integrated |

| SIMD | None |

| Fab | 800 – 1000 nm |

| Transistor Count | 1,185,000 |

| Power Consumption | N/A |

| Voltage | 5V – 3.3V |

| Die Area | 67-81 mm2 |

| Socket | 168 pins |

After the release of the Pentium series, AMD too geared up to introduce the “Pentium Rating System”. The 133 MHz AMD AM5x86 was a higher clocked enhanced Am486.

AMD AM5x86

| Release Date | 1995 |

| Architecture | 32 -bit |

| Data Bus | 32 -bit |

| Address Bus | 32 -bit |

| Maximum Memory Support | 4 Gb |

| L1 Cache | 16 KB |

| L2 Cache | None |

| Frequency | 133 – 150 MHz |

| FSB | 33 – 50 MHz |

| FPU | Integrated |

| SIMD | None |

| Fab | 350 nm |

| Transistor Count | N/A |

| Power Consumption | N/A |

| Voltage | 3.45 V |

| Die Area | N/A |

| Socket | 168 pins |

K5: AMD First Own x86 Processor

In the year of 1966 AMD released its in-house designed x86 processor. The fifth gen x86 K5 processor used the execution hardware from the discontinued AM29000 RISC processor with an x86 frontend. Since the execution back end hardware was based on RISC design, Instructions were encoded into micro-instructions and fed into one of five integer execution units or an integrated FPU.

AMD implemented such a design which limited the clock speed. As a result K5 was not able to surpass Intel’s Pentium in terms of performance. It was considered relatively efficient.

| Release Date | 1996 |

| Architecture | 32 –bit |

| Data Bus | 32 –bit |

| Address Bus | 32 –bit |

| Maximum Memory Support | 4 Gb |

| L1 Cache | 16 KB + 8 KB |

| L2 Cache | None |

| SIMD | None |

| FSB | 50 – 66 MHz |

| SIMD | None |

| Fab | 350 – 500 nm |

| Transistor Count | 4.3 Million |

| Power Consumption | 11 – 16 W |

| Voltage | 3.52 V |

| Die Area | 181 – 251 mm2 |

| Connection | Socket 5 & Socket 7 |

AMD K6 processor

This microprocessor was launched in 1997. Its main advantage was that it could fit into existing desktop design for Pentium-branded CPUs.

The AMD K6 is based on the Nx686 microprocessor that NexGen was designing, when it was acquired by AMD. Initially it launched at 166 – 200MHz, followed by 233 MHz version. Initially the AMD K6 processor used Pentium II-based performance rating, which was later dropped because the rated frequency of the processor was the same as the real frequency.

The K6 was compatible with Socket7 motherboards; clock-for-clock. It included the important MMX SIMD instruction set.

| Date | 1997/1998 |

| Architecture | 32-bit |

| Data Bus | 32-bit |

| Address Bus | 32-bit |

| Maximum Memory Support | 4GB |

| L1 Cache | 32 KB + 32 KB |

| L2 Cache | None |

| L3 Cache | None |

| Clock Speed | 266 -350 MHz |

| FSB | 50 – 66 MHz |

| SIMD | MMX |

| FAB | 350 – 250 nm |

| Transistor Count | 8.8 Million |

| Power Consumption | 12 – 28 W |

| Voltage | 2.2 – 3.2 V |

| Die Area | 68 – 157 mm2 |

| Socket | Socket 7 |

AMD K6-II

AMD next processor was the K6 II, which was eventually an extended version of the K6. It used a faster 100MHz FSB, higher clock speeds and a new SIMD instruction. SIMD instruction set as a competitor to Intel’s MMX, and gave customers an upgrade from the aging Pentium MMX processors.

| Date | 1998 |

| Architecture | 32-bit |

| Data Bus | 32-bit |

| Address Bus | 32-bit |

| Maximum Memory Support | 4GB |

| L1 Cache | 32 KB + 32 KB |

| L2 Cache | None |

| L3 Cache | None |

| Clock Speed | 300 -550 MHz |

| FSB | 66 – 100 MHz |

| SIMD | MMX, 3DNow! |

| FAB | 250 nm |

| Transistor Count | 9.3 Million |

| Power Consumption | 13 – 25 W |

| Voltage | 2.2 – 2.4 W |

| Die Area | 81 mm2 |

| Socket | Socket 7/Super Socket7 |

AMD K6-III: The Integration of L2 Cache

The K6-III was a K6-2 core with full speed 256Kib L2 cache integrated on the same die. This integration reduced latency and increased bandwidth. AMD however quickly replaced it with the Athlon processor.

| Date | 1999 |

| Architecture | 32-bit |

| Data Bus | 32-bit |

| Address Bus | 32-bit |

| Maximum Memory Support | 4GB |

| L1 Cache | 32 KB + 32 KB |

| L2 Cache | 256 KB |

| L3 Cache | None |

| Clock Speed | 350 – 550 MHz |

| FSB | 100 MHz |

| SIMD | MMX, 3DNow! |

| FAB | 250 nm |

| Transistor Count | 21.3 Million |

| Power Consumption | 10 – 17 W |

| Voltage | 2.2 – 2.4 W |

| Die Area | 118 mm2 |

| Socket | Super Socket7 |

AMD K6-II+ and K6-III+

The last processors released by AMD in the K6 product line were the K6-II+ and the K6-III+. These processors were targeted at the mobile market. The K6II+ had 128 KB of L2 cache whereas the K6-III+ had 256 KB of L2 cache. AMD 180nm fab technology resulted that these processors became energy efficient.

| Date | 2000 |

| Architecture | 32-bit |

| Data Bus | 32-bit |

| Address Bus | 32-bit |

| Maximum Memory Support | 4GB |

| L1 Cache | 32 KB + 32 KB |

| L2 Cache | 128 Kb – 256 KB |

| L3 Cache | None |

| Clock Speed | 400 – 500 MHz |

| FSB | 100 MHz |

| SIMD | MMX, 3DNow! |

| FAB | 180 nm |

| Transistor Count | N/A |

| Power Consumption | N/A |

| Voltage | 1.6 – 2.0 W |

| Die Area | N/A |

| Socket | N/A |

AMD K7 and K75

In 1988 AMD partnered with Semiconductor giant Motorola to co-develop copper based semiconductor technology. This resulted in the K7 project being first commercial processor to use copper fabrication technology .The K7 design team consisted of the previously acquired NexGen K6 team and the new Alpha design team.

In 1999, AMD released its seventh-generation processor, the Athlon. The Athlon microarchitecture used a separate L-2 cache chip on board. A new extended MMX was also introduced. In the second generation the L2 cache was integrated. The new architecture increased IPC and pushed the clock speed to 1 GHz. Previously the FPU lagged behind Intel’s. This time it was improved.

AMD K7

| Date | June 1999 |

| Architecture | 32-bit |

| Data Bus | 32-bit |

| Address Bus | 32-bit |

| Maximum Memory Support | 4GB |

| L1 Cache | 64 KB + 64 KB |

| L2 Cache | 512 KB |

| L3 Cache | None |

| Clock Speed | 500 – 700 MHz |

| FSB | 100 MHz |

| SIMD | MMX, 3DNow! |

| FAB | 250 nm |

| Transistor Count | 22 Million |

| Power Consumption | 31 – 65 W |

| Voltage | 1.6 – 1.8 W |

| Die Area | 102 mm2 |

| Socket | Slot A |

AMD K75

| Date | Nov 1999 |

| Architecture | 32-bit |

| Data Bus | 32-bit |

| Address Bus | 32-bit |

| Maximum Memory Support | 4GB |

| L1 Cache | 64 KB + 64 KB |

| L2 Cache | 512 KB |

| L3 Cache | None |

| Clock Speed | 550 – 850 MHz |

| FSB | 100 MHz |

| SIMD | MMX, 3DNow! |

| FAB | 180 nm |

| Transistor Count | 22 Million |

| Power Consumption | 31 – 65 W |

| Voltage | 1.6 – 1.8 W |

| Die Area | 102 mm2 |

| Socket | Slot A |

AMD K7: Athlon Thunderbird

AMD team realised that that the dull performance of thee L2 cache was hampering the CPU performance. This version of Athlon shipped in a traditional pin-grid array format that plugged into a socket on the motherboard. Although L2 cache size as cut to half, it ran at the same speed as the CPU, thereby improving the performance drastically.

| Date | 2000 |

| Architecture | 32-bit |

| Data Bus | 32-bit |

| Address Bus | 32-bit |

| Maximum Memory Support | 4GB |

| L1 Cache | 64 KB + 64 KB |

| L2 Cache | 256 KB |

| L3 Cache | None |

| Clock Speed | 600 – 1400 MHz |

| FSB | 100, 133 MHz |

| SIMD | MMX, 3DNow! |

| FAB | 180 nm |

| Transistor Count | 37 Million |

| Power Consumption | 38 – 72 W |

| Voltage | 1.7 – 1.75 W |

| Die Area | 120 mm2 |

| Socket | Socket A |

AMD Duron

The Duron processor was derived from the mainstream Athlon Thunderbird processor. Duron was introduced as a budget line x86 compatible processor. These processors ran at lower clock speeds.

| Date | 2000/2001 |

| Architecture | 32-bit |

| Data Bus | 32-bit |

| Address Bus | 32-bit |

| Maximum Memory Support | 4GB |

| L1 Cache | 64 KB + 64 KB |

| L2 Cache | 64 KB |

| L3 Cache | None |

| Frequency | 600 – 950 MHz |

| FSB | 100 |

| SIMD | MMX, 3DNow! |

| FAB | 180 nm |

| Transistor Count | 37 Million |

| Power Consumption | N/A |

| Voltage | 1.5 – 1.75 W |

| Die Area | 120 mm2 |

| Socket | Socket A |

AMD K7: Athlon Palomino

AMD released the third generation Athlon, code-named “Palomino”, on 2001 as Athlon XP. This “XP” was used to mean extended performance and also as an unofficial reference to the Windows XP. AMD pushed the clock speed even higher to 333MHz, and also added the support of SSE SIMD instruction set.

| Date | May 2001 |

| Architecture | 32-bit |

| Data Bus | 32-bit |

| Address Bus | 32-bit |

| Maximum Memory Support | 4GB |

| L1 Cache | 64 KB + 64 KB |

| L2 Cache | 256 KB |

| L3 Cache | None |

| Frequency | 850 – 1733 MHz |

| FSB | 133 MHz |

| SIMD | MMX, 3DNow! |

| FAB | 180 nm |

| Transistor Count | 37.5 Million |

| Power Consumption | 46 – 72 W |

| Voltage | 1.75 W |

| Die Area | 129.26 mm2 |

| Socket | Socket A |

AMD K7: Athlon Thoroughbred

AMD released the fourth generation of Athlon with the Thoroughbred core. It was released on June 10, 2002. Thoroughbred was AMD’s first 130 nm based Die size.

The core was referred to as Tbred, there were two versions the Tbred-A and the Tbred-B. the Tbred-A was based on preceding Palomino core with minimal design changes. The reduced Die size resulted in lower power consumption and pushed frequencies to 2GHz.

| Date | April 2002 |

| Architecture | 32-bit |

| Data Bus | 32-bit |

| Address Bus | 32-bit |

| Maximum Memory Support | 4GB |

| L1 Cache | 64 KB + 64 KB |

| L2 Cache | 256 KB |

| L3 Cache | None |

| Frequency | 1 – 2.25 GHz |

| FSB | 100 – 166 MHz |

| SIMD | MMX, 3DNow!, SSE |

| FAB | 130 nm |

| Transistor Count | 37.2 Million |

| Power Consumption | 49 – 68 W |

| Voltage | 1.5 – 1.65 W |

| Die Area | 84.66 mm2 |

| Socket | Socket A |

AMD K7: Athlon Barton

AMD released the fifth generation Athlon Barton processor in 2003. These processors were marked at higher PR rating rather than with increased clock speed compared to the Thoroughbred.

Barton processors doubled the size of L2 cache and added support for 200 MHz FSB and 400 MHz DDR RAM.

| Date | Feb 2003 |

| Architecture | 32-bit |

| Data Bus | 32-bit |

| Address Bus | 32-bit |

| Maximum Memory Support | 4GB |

| L1 Cache | 64 KB + 64 KB |

| L2 Cache | 512 KB |

| L3 Cache | None |

| Frequency | 1.3 – 2.33 GHz |

| FSB | 100 – 200 MHz |

| SIMD | MMX, 3DNow!, SSE |

| FAB | 130 nm |

| Transistor Count | 54.3 Million |

| Power Consumption | 60 – 76 W |

| Voltage | 1.65 W |

| Die Area | 100.99 mm2 |

| Socket | Socket A |

AMD Athlon Thorton and Duron

Thorton was released as a variant of Barton with half of L2 cache disabled. Both Thorton and Barton were released as two lower -end processors.

Thorton had 256 KB of L2 cache and ran at a higher clock speed than Barton. The Duron had only 64 KB of L2 cache and ran at 1.8 GHz.

AMD Athlon Thorton and Duron

| Date | 2003 | 2003 |

| Architecture | 32-bit | 32-bit |

| Data Bus | 32-bit | 32-bit |

| Address Bus | 32-bit | 32-bit |

| Maximum Memory Support | 4GB | 4GB |

| L1 Cache | 64 KB + 64 KB | 64 KB + 64 KB |

| L2 Cache | 256 KB | 64 KB |

| L3 Cache | None | None |

| Frequency | 1.66 – 2.2 GHz | .41 – 1.8 GHz |

| FSB | 100 – 200 MHz | 133 MHz |

| SIMD | MMX, 3DNow!, SSE | MMX, 3DNow!, SSE |

| FAB | 130 nm | 130 nm |

| Transistor Count | 54.3 Million | 54.3 Million |

| Power Consumption | N/A | N/A |

| Voltage | 1.5 – 1.65 W | 1.5 W |

| Die Area | 100.99 mm2 | 100.99 mm2 |

| Socket | Socket A | Socket A |

AMD Geode

Geode was released to target at the embedded computing market. The original Geode processor was derived from the Cyrix MediaGX platform. AMD bought the Geode business from national in 2003 and extended it low-end product offering.

AMD launched two processors under the “Geode” name at the low-end AMD introduced the GX series whereas for higher performance LX series was launched.

AMD Geode GX-Series

| Date | 2003 |

| Architecture | 32-bit |

| Data Bus | 32-bit |

| Address Bus | 32-bit |

| Maximum Memory Support | 4GB |

| L1 Cache | 16 KB |

| L2 Cache | N/A |

| L3 Cache | None |

| Frequency | 333 – 400 MHz |

| FSB | N/A |

| SIMD | N/A |

| FAB | N/A |

| Transistor Count | N/A |

| Power Consumption | N/A |

| Voltage | N/A |

| Die Area | N/A |

| Socket | N/A |

AMD Geode LX-Series

| Date | 2003 |

| Architecture | 32-bit |

| Data Bus | 32-bit |

| Address Bus | 32-bit |

| Maximum Memory Support | 4GB |

| L1 Cache | 64 KB + 64 KB |

| L2 Cache | 128 KB |

| L3 Cache | None |

| Frequency | 366 – 600 MHz |

| FSB | N/A |

| SIMD | N/A |

| FAB | 130 nm |

| Transistor Count | N/A |

| Power Consumption | N/A |

| Voltage | N/A |

| Die Area | N/A |

| Socket | N/A |

AMD K7: First Sempron

The Sempron was introduced to compete with the Intel’s Celeron processor. The Sempron was a daily use processor. It CPU was based on the Athlon XP architecture using the Thoroughbred core. It used 256 KB of L2 cache.

| Name | Throton | Barton |

| Date | July 2004 | Sep 2004 |

| Architecture | 32-bit | 32-bit |

| Data Bus | 32-bit | 32-bit |

| Address Bus | 32-bit | 32-bit |

| Maximum Memory Support | 4GB | 4GB |

| L1 Cache | 64 KB + 64 KB | 64 KB + 64 KB |

| L2 Cache | 256 KB | 256 KB |

| L3 Cache | None | None |

| Frequency | 1.5 – 2.0 GHz | 2 – 2.2 GHz |

| FSB | 166 MHz | 166 – 200 MHz |

| SIMD | MMX, 3DNow!, SSE | MMX, 3DNow!, SSE |

| FAB | 130 nm | 130 nm |

| Transistor Count | 37.2 – 54.3 Million | 54.3 Million |

| Power Consumption | N/A | N/A |

| Voltage | 1.6 W | 1.6 – 1.65 W |

| Die Area | 84.66 – 100.99

mm2 |

100.99 mm2 |

| Socket | Socket A | Socket A |

AMD K8: Athlon 64

AMD Athlon 64 was the first 64-bit processor targeted at the consumer level. Since I was a 64-bit deign the memory support was extended to 1 TB. The Pcs were no longer limited to 4GB of memory and 8GB of RAM. AMD also moved the memory controller from its chipset and integrate it to the CPU die. As a result memory latency reduced and performance got jumped up.

This thing removed the FS from the system and instead AMD introduced its HyperTransport technology, which was of a greter bandwidth than the FSB connection.

AMD Athlon 64 Sledgehammer

| Date | 2003/2004 |

| Architecture | 64-bit |

| Data Bus | 64-bit |

| Address Bus | 64-bit |

| Maximum Memory Support | 1TB |

| L1 Cache | 64 KB + 64 KB |

| L2 Cache | 1 MB |

| Hyper Transport | 800 MHz |

| Clock Speed | 1.4 – 2.4 GHz |

| Memory Controller | Single channel 400 MHz DDR |

| SIMD | MMX, Enhanced3DNow!

SSE,SSE2 |

| FAB | 130 nm |

| Transistor Count | 105.9 Million |

| Power Consumption | 89 W TDP |

| Voltage | 1.5 – 1.55 V |

| Die Area | 193 mm2 |

| Socket | Socket 940 |

AMD Athlon Newcastle/Clawhammer

| Date | 2004 |

| Architecture | 64-bit |

| Data Bus | 64-bit |

| Address Bus | 64-bit |

| Maximum Memory Support | 1TB |

| L1 Cache | 64 KB + 64 KB |

| L2 Cache | 512 KB(Newcastle),1MB(Clawhammer) |

| Hyper Transport | 800 – 1000 MHz |

| Clock Speed | 1.8 – 2.4 GHz |

| Memory Controller | Single channel 400 MHz DDR |

| SIMD | MMX, Enhanced3DNow!

SSE,SSE2 |

| FAB | 130 nm |

| Transistor Count | 105.9 Million |

| Power Consumption | 89 W TDP |

| Voltage | 1.5 – 1.55 V |

| Die Area | 193 mm2 |

| Socket | Socket 754, Socket 939 |

AMD K8

The change from K7 to K8 is the integration of AMD64 instructions and the on-chip memory controller. The memory controller reduces memory latency and improves performance. It was introduced in 2004 with 90nm die area. Venice was the last Athlon 64 processor released by AMD. It was compatible with the AMD’s Socket 754. Orleans was released in 2006 which was most energy efficient with 62 W TDP.

AMD Athlon 64 Venice

| Date | 2005 |

| Architecture | 64-bit |

| Data Bus | 64-bit |

| Address Bus | 64-bit |

| Maximum Memory Support | 1TB |

| L1 Cache | 64 KB + 64 KB |

| L2 Cache | 512 KB |

| Hyper Transport | 800 MHz |

| Clock Speed | 1.8 – 2.2 GHz |

| Memory Controller | Single Channel 400 MHz DDR |

| SIMD | MMX, Enhanced3DNow!

SSE,SSE2,SSE3 |

| FAB | 90 nm |

| Transistor Count | N/A |

| Power Consumption | 64 W TDP |

| Voltage | 1.35 – 1.4 V |

| Die Area | N/A |

| Socket | Socket 754 |

AMD Athlon Orleans

| Date | 2006 |

| Architecture | 64-bit |

| Data Bus | 64-bit |

| Address Bus | 64-bit |

| Maximum Memory Support | 1TB |

| L1 Cache | 64 KB + 64 KB |

| L2 Cache | 1 MB |

| Hyper Transport | 800-1000 MHz |

| Clock Speed | 1.4 – 2.6 GHz |

| Memory Controller | Dual-Channel DDR2 |

| SIMD | MMX, Enhanced3DNow!

SSE,SSE2,SSE3 |

| FAB | 90 nm |

| Transistor Count | 105.9 Million |

| Power Consumption | 62 W TDP |

| Voltage | 1.25 – 1.4 V |

| Die Area | N/A |

| Socket | Socket AM2 |

AMD K8: Sempron

The first Sempron was based on the AMD Athlon XP architecture. AMD updated this new Sempron architecture, but with less cache and clock speeds.

AMD K8 Sempron

| Date | 2004 -2007 |

| Architecture | 64-bit |

| Data Bus | 64-bit |

| Address Bus | 64-bit |

| Maximum Memory Support | 1TB |

| L1 Cache | 64 KB + 64 KB |

| L2 Cache | 128 KB – 512 KB |

| Hyper Transport | 800/1000 MHz |

| Clock Speed | 1.4 – 2.3 GHz |

| Memory Controller | Single channel DDR/Dual Channel DDR/Dual ChannelDDR2 |

| SIMD | MMX, Enhanced3DNow!

SSE,SSE2 |

| FAB | 130 – 65 nm |

| Transistor Count | N/A |

| Power Consumption | N/A |

| Voltage | 1.2 – 1.4 V |

| Die Area | N/A |

| Socket | Socket 754/Socket939/SocketAM2 |

AMD K8: Athlon 64 X2

The Athlon 64 X2 was designed from scratch as a dual core by using a multi-CPU enabled Athlon 64, joining it with another functional core on one die and connecting both via a shared dual-channel memory.

The two processors were incapable of working on the same thread simultaneously. The second core would handle other tasks and increase multitasking performance. AMD produced a total number of six configurations, the sixth configuration was the fastest and the most energy efficient. It had a 65 nm technology.

| Name | Manchester-Windsor | Brisbane |

| Date | 2005 – 2006 | 2006 |

| Architecture | 64-bit | 64-bit |

| Data Bus | 64-bit | 64-bit |

| Address Bus | 64-bit | 64-bit |

| Maximum Memory Support | 1 Tb | 1 TB |

| L1 Cache | 64 KB + 64 KB | 64 KB + 64 KB |

| L2 Cache | 256 KB | 512 KB |

| L3 Cache | None | None |

| Frequency | 2 – 3.2 GHz | 1.9– 3.1 GHz |

| Memory controller | Dual Channel DDR/DDR2 | Dual channel DDR2 |

| SIMD | MMX, 3DNow!, SSE,SSE2,SSE3 | MMX, 3DNow!, SSE,SSE2,SSE3 |

| FAB | 90 nm | 65 nm |

| Transistor Count | N/A | N/A |

| Power Consumption | 35 – 125 W TDP | 65 – 89 W TDP |

| Voltage | 1.25 – 1.4 V | 1.25 – 1.35 V |

| Die Area | N/A | 126 mm2 |

| Socket | Socket 939, Socket AM2 | Socket AM2 |

AMD K8: Turion and Turion X2

AMD introduced this as a new mobile product line called “Turion”. Due to core binding it could operate with less power. The Turion X2 was a dual core variant

| Name | Turion | Turion X2 |

| Date | 2005 – 2008 | 2006 – 2008 |

| Architecture | 64-bit | 64-bit |

| Data Bus | 64-bit | 64-bit |

| Address Bus | 64-bit | 64-bit |

| Maximum Memory Support | 1 Tb | 1 TB |

| L1 Cache | 64 KB + 64 KB | 64 KB + 64 KB |

| L2 Cache | 512 KB – 1 MB | 256 KB – 1 MB |

| L3 Cache | None | None |

| Frequency | 1.6 – 2.4 GHz | 1.6– 2.5 GHz |

| Memory controller | Single Channel DDR/Dual Channel DDR2 | Dual channel DDR2 |

| SIMD | MMX, 3DNow!, SSE,SSE2,SSE3 | MMX, 3DNow!, SSE,SSE2,SSE3 |

| FAB | 65-90 nm | 65-90 nm |

| Transistor Count | N/A | N/A |

| Power Consumption | 25 – 35 W TDP | 31 – 35 W TDP |

| Voltage | 0.8 – 1.35 V | N/A |

| Die Area | N/A | N/A |

| Socket | Socket 754, Socket S1 | Socket S1 |

AMD K10

The AMD K10 is a processor based on the K8 microarchitecture. In 2003 AMD wanted to implement some outlined features for the next-gen microprocessors. These features included were

Threaded architecture, Chip level multiprocessing, huge scale MP, 10GHz operation etc…

The first K10 processor was based on Barcelona configuration and sold as Opteron server processors. A TLB bug was detected which would lock up the CPU, but soon AMD released a software to solve it. The fastest quad-core model was limited to 2.6 GHz, whereas K10 processors under Athlon reached to 2.8 GHz.

| Name | Agena | Toliman |

| Date | Nov 2007 | March 2008 |

| Architecture | 64-bit | 64-bit |

| Data Bus | 64-bit | 64-bit |

| Address Bus | 64-bit | 64-bit |

| Maximum Memory Support | 1 Tb | 1 TB |

| L1 Cache | 64 KB + 64 KB | 64 KB + 64 KB |

| L2 Cache | 512 KB | 512 KB |

| Hyper transport | 2000 MHz | 2000 MHz |

| Frequency | 1.8 – 2.6 GHz | 1.9– 2.5 GHz |

| Memory controller | Dual Channel DDR2 | Dual channel DDR2 |

| SIMD | MMX, 3DNow!, SSE,SSE2,SSE3,SSE4a | MMX, 3DNow!, SSE,SSE2,SSE3,SSE4a |

| FAB | 65 nm | 65 nm |

| Transistor Count | 450 Million | 450 Million |

| Power Consumption | 65 – 140 W TDP | 65 – 95 W TDP |

| Core Count | 4 | 3 |

| Voltage | 1.25 – 1.4 V | 1.25 – 1.35 V |

| Die Area | 285 mm2 | 285 mm2 |

| Socket | Socket AM2/AM2+ | Socket AM2+ |

AMD K10: Phenom II

The Phenom II was launched with a die area of 45 nm. It used the same architecture as the AMD K10. As a result of the 45nm process, power consumption dropped, as also the amount of heat released. This resulted in higher clock speed of about 3.7 GHz. Since the size of die was small AMD was able to triple the L3 cache.

AMD Phenom II X4

| Date | Jan 2009 |

| Architecture | 64-bit |

| Data Bus | 64-bit |

| Address Bus | 64-bit |

| Maximum Memory Support | 1TB |

| L1 Cache | 64 KB + 64 KB |

| L2 Cache | 1 MB |

| L3 Cache | 6 MB |

| Hyper Transport | 2000 MHz |

| Clock Speed | 2.6 – 3.7 GHz |

| Memory Controller | Dual-Channel DDR2 |

| SIMD | MMX, Enhanced3DNow!

SSE,SSE2,SSE3,SSE4a |

| FAB | 45 nm |

| Transistor Count | 758 Million |

| Power Consumption | 65 – 140 W TDP |

| Voltage | 1.4 V |

| Die Area | 243 mm2 |

| Socket | Socket AM2+/AM3 |

AMD K10: Phenom II X2 and X3

AMD recycled its semi-defective quad-core CPU die as a triple and dual core dies. These processors had the 6MB of L3 Cache but ran at lower clock speeds.

| Name | Heka | Callisto |

| Date | Feb 2009 | June 2009 |

| Architecture | 64-bit | 64-bit |

| Data Bus | 64-bit | 64-bit |

| Address Bus | 64-bit | 64-bit |

| Maximum Memory Support | 1 Tb | 1 TB |

| L1 Cache | 64 KB + 64 KB | 64 KB + 64 KB |

| L2 Cache | 512 KB | 512 KB |

| Hyper transport | 2000 MHz | 2000 MHz |

| Clock Speed | 2.4 – 3.2 GHz | 2.8– 3.5 GHz |

| Memory controller | Dual Channel DDR2,Dual- Channel DDR3 | Dual channel DDR2,Dual-ChannelDDR3 |

| SIMD | MMX, 3DNow!, SSE,SSE2,SSE3,SSE4a | MMX, 3DNow!, SSE,SSE2,SSE3,SSE4a |

| FAB | 65 nm | 65 nm |

| Transistor Count | 758 Million | 758 Million |

| Power Consumption | 65 – 95 W TDP | 80 W TDP |

| Core Count | 3 | 2 |

| Voltage | 1.4 V | 1.4 V |

| Die Area | 243 mm2 | 243 mm2 |

| Socket | SockeAM2+/AM3 | Socket AM2+/AM3 |

AMD K10: Athlon II

AMD introduced low-end processors branded Athlon II. To cut the production cost L3 was discontinued here. The quad-core die was named Propus whereas the Triple-core was named Regor.

AMD Athlon II

| Name | Propus | Regor |

| Date | Sept 2009 | June 2009 |

| Architecture | 64-bit | 64-bit |

| Data Bus | 64-bit | 64-bit |

| Address Bus | 64-bit | 64-bit |

| Maximum Memory Support | 1 Tb | 1 TB |

| L1 Cache | 64 KB + 64 KB | 64 KB + 64 KB |

| L2 Cache | 512 KB | 512 KB |

| Hyper transport | 2000 MHz | 2000 MHz |

| Frequency | 2.2 – 3.2GHz | 2.8 – 3.6 GHz |

| Memory controller | Dual Channel DDR2,Dual-ChannelDDR3 | Dual channel DDR2,Dual-ChannelDDr3 |

| SIMD | MMX, 3DNow!, SSE,SSE2,SSE3,SSE4a | MMX, 3DNow!, SSE,SSE2,SSE3,SSE4a |

| FAB | 45 nm | 45 nm |

| Transistor Count | N/A | 234 Million |

| Power Consumption | 45 – 95 W TDP | 25 – 65 W TDP |

| Core Count | 4 | 2 |

| Voltage | 1.25 – 1.4 V | 1.25 – 1.35 V |

| Die Area | 285 mm2 | 285 mm2 |

| Socket | SocketAM2+/AM3 | Socket AM2+/AM3 |

AMD K10: Sempron

AMD extended its Sempron line to serve the lowest-performance product in the K10 line. The K10 Sempros was developed from the single-core Sargas die which was built from defective Regor core.

| Date | July 2009 |

| Architecture | 64-bit |

| Data Bus | 64-bit |

| Address Bus | 64-bit |

| Maximum Memory Support | 1TB |

| L1 Cache | 64 KB + 64 KB |

| L2 Cache | 1 MB |

| L3 Cache | None |

| Hyper Transport | 2000 MHz |

| Clock Speed | 1.8 –2.9 GHz |

| Memory Controller | Dual-Channel DDR2, Dual-ChannelDDr3 |

| SIMD | MMX, Enhanced3DNow!

SSE,SSE2,SSE3,SSE4a |

| FAB | 45 nm |

| Transistor Count | 234 Million |

| Power Consumption | 65 – 140 W TDP |

| Voltage | 1.3 V |

| Die Area | 117 mm2 |

| Socket | Socket AM2+/AM3 |

AMD K10: Phenom II X6

In 2010 AMD lifted its K10 product line by introducing the Thuban and the Zosma CPU dies. The thuban consisted of a total six cores and clocked it as high as 3.3 GHz.AMD introduced Turbo Core technology which allowed to push the clock speed even further to 3.7 GHZ.

| Name | Thuban | Zosma |

| Date | 2010 | 2010 |

| Architecture | 64-bit | 64-bit |

| Data Bus | 64-bit | 64-bit |

| Address Bus | 64-bit | 64-bit |

| Maximum Memory Support | 1 Tb | 1 TB |

| L1 Cache | 64 KB + 64 KB | 64 KB + 64 KB |

| L2 Cache | 512 KB | 512 KB |

| L3 Cache | 6 MB | 6MB |

| Hyper transport | 2000 MHz | 2000 MHz |

| Clock Speed | 2.4 – 3.3 GHz | 2.7– 3.5 GHz |

| Memory controller | Dual Channel DDR2,Dual- Channel DDR3 | Dual channel DDR2,Dual-ChannelDDR3 |

| SIMD | MMX, 3DNow!, SSE,SSE2,SSE3,SSE4a | MMX, 3DNow!, SSE,SSE2,SSE3,SSE4a |

| FAB | 45 nm | 45 nm |

| Transistor Count | 904 Million | 904 Million |

| Power Consumption | 95 – 125 W TDP | 95 – 125 W TDP |

| Core Count | 6 | 4 |

| Voltage | 1.4 V | 1.4 V |

| Die Area | 346 mm2 | 346 mm2 |

| Socket | SocketAM3 | SocketAM3 |

AMD Bobcat

The Bobcat was aimed at low power/low-cost market. It was implemented in AMD APU processor with a TDP of 18 W or less. Since Bobcat was designed to be efficient it ran at fairly lower clock speed of 1.75 GHz. Bobcat is technically an APU with 80 stream of iGPU. The processor based on a Terascale 2.

AMD Bobcat

| Date | 2011 |

| Architecture | 64-bit |

| Data Bus | 64-bit |

| Address Bus | 64-bit |

| Maximum Memory Support | 1TB |

| L1 Cache | 32 KB + 32 KB |

| L2 Cache | 512 KB |

| Core Count | 1 – 2 |

| Hyper Transport | 2000 MHz |

| Clock Speed | 0.8 –1.75 GHz |

| Memory Controller | Single-Channel DDR3L |

| SIMD | MMXSSE,SSE2,SSE3,SSE4.1/4.2 |

| FAB | 40 nm |

| Transistor Count | N/A |

| Power Consumption | 4.5 – 18 W TDP |

| Voltage | 0.5 – 1.4 V |

| Die Area | 107 mm2 |

| Socket | AM1 |

AMD Bulldozer: Zambezi

The bulldozer was developed from scratch. It was aimed to computing products with TDP 10 – 125 W. Bulldozer attempted to use a high core count and clock speed to outperform Intel’s Sandy Bridge.

AMD Bulldozer Zambezi

| Date | Oct 2011 |

| Architecture | 64-bit |

| Data Bus | 64-bit |

| Address Bus | 64-bit |

| Maximum Memory Support | 1TB |

| L1 Cache | 64 KB + 64 KB |

| L2 Cache | 2 MB |

| L3 Cache | 8 MB |

| Core | 4,6,8 |

| Hyper Transport | 2600 MHz |

| Clock Speed | 2.8 –4.2 GHz |

| Memory Controller | Dual-ChannelDDr3 |

| SIMD | MMX,SSE,SSE2,SSE3,SSE4.1/4.2 |

| FAB | 32 nm |

| Transistor Count | N/A |

| Power Consumption | 95 – 125 W TDP |

| Voltage | 0.95 – 1.4125 V |

| Die Area | 316 mm2 |

| Socket | SocketAM3 |

AMD Piledriver: Trinty and Richland

After a year bulldozer debuted, AMD released a new architecture called the Piledriver. It was initially released with the company’s second gen APU. The clockspeed increased by 10 percent.

| Name | Trinity | Richland |

| Date | 2012 | 2013 |

| Architecture | 64-bit | 64-bit |

| Data Bus | 64-bit | 64-bit |

| Address Bus | 64-bit | 64-bit |

| Maximum Memory Support | 1 Tb | 1 TB |

| L1 Cache | 64 KB + (2×16) KB | 64 KB + (2×16) KB |

| L2 Cache | 2 MB | 2 MB |

| L3 Cache | N/A | N/A |

| Hyper transport | 2000 MHz | 2000 MHz |

| Clock Speed | 2.9 – 3.8 GHz | 2.1– 4.1 GHz |

| Memory controller | Dual- Channel DDR3 | Dual-ChannelDDR3 |

| SIMD | MMX,SSE,SSE2,SSE3,SSE4a, SSE4.1/4.2,AVX | MMX,SSE,SSE2,SSE3,SSE4a,SSE4.1/4.2 |

| FAB | 32 nm | 32 nm |

| Transistor Count | 1300 Million | 1300 Million |

| Power Consumption | 65 – 100 W TDP | 45 – 100 W TDP |

| Core Count | 2 – 4 | 2 – 4 |

| Voltage | 0.825 – 1.475 V | N/A |

| Die Area | 346 mm2 | 346 mm2 |

| Socket | SocketAM3 | SocketAM3 |

AMD Steamroller: A GCN APU

AMD updated its APU line with a new Steamroller architecture which succeeded Piledriver. Steamroller focused on parallelism. AMD improved the instruction percycle to 30% which with decreased power increaded the performance.

| Name | Kaveri | Godavari |

| Date | 2014 | 2015 |

| Architecture | 64-bit | 64-bit |

| Data Bus | 64-bit | 64-bit |

| Address Bus | 64-bit | 64-bit |

| Maximum Memory Support | 1 Tb | 1 TB |

| L1 Cache | 96 KB + (2×16) KB | 96 KB + (2×16) KB |

| L2 Cache | 2 MB | 2 MB |

| L3 Cache | N/A | N/A |

| Hyper transport | 2000 MHz | 2000 MHz |

| Clock Speed | 3.1 – 3.7 GHz | 2.9 – 3.9 GHz |

| Memory controller | Dual- Channel DDR3 | Dual-ChannelDDR3 |

| SIMD | MMX,SSE,SSE2,SSE3,SSE4a, SSE4.1/4.2,AVX | MMX,SSE,SSE2,SSE3,SSE4a,SSE4.1/4.2 |

| FAB | 28 nm | 28 nm |

| Transistor Count | 2.41 Billion | 2.41 Billion |

| Power Consumption | 65 – 95 W TDP | 65 – 95 W TDP |

| Core Count | 2 – 4 | 2 – 4 |

| Voltage | N/A | N/A |

| Die Area | 245 mm2 | N/A |

| Socket | GCN Radeon R5/R7 | GCN Radeon R5/R7 |

AMD Jaguar

The Jaguar architecture was released in 2014 to replace the aging Bobcat. The CPU count was increased by four and moved to a faster GCN- based graphic processor. IPC was raised by 15% with a boost in clock speed.

| Date | 2014 |

| Architecture | 64-bit |

| Data Bus | 64-bit |

| Address Bus | 64-bit |

| Maximum Memory Support | 1TB |

| L1 Cache | 32 KB + 32 KB |

| L2 Cache | 512 KB |

| L3 Cache | None |

| Core | 2 – 4 |

| iGPU architecture | GCN Radeon R3 |

| Clock Speed | 2.8 –4.2 GHz |

| Memory Controller | Dual-Channel DDr3 |

| SIMD | MMX,SSE,SSE2,SSE3,SSE4.1/4.2,AVX |

| FAB | 28 nm |

| Transistor Count | N/A |

| Power Consumption | 3.9 – 25 W TDP |

| Voltage | 0.5 – 1.4 V |

| Die Area | 107 mm2 |

| Socket | AM1 |

AMD Excavator

Excavator was the last processor whose architecture was based on Bulldozer. The processor had less L2 cache but twice as much as L1cache. Since the L1 cache was faster than L2 cache it helped boost the IPC performance. The graphic processor also gain some 512 KB of dedicated L2 cache to increase graphic processing power.

| Date | 2015 |

| Architecture | 64-bit |

| Data Bus | 64-bit |

| Address Bus | 64-bit |

| Maximum Memory Support | 1TB |

| L1 Cache | 192 KB + (2×32) KB |

| L2 Cache | 1 MB |

| L3 Cache | None |

| Core | 2 – 4 |

| iGPU architecture | GCN Radeon R3 |

| Clock Speed | 2.8 –4.2 GHz |

| Memory Controller | Dual-Channel DDr3 |

| SIMD | MMX,SSE,SSE2,SSE3,SSE4.1/4.2,AVX,AVX |

| FAB | 28 nm |

| Transistor Count | N/A |

| Power Consumption | 65 W TDP |

| Voltage | N/A |

| Die Area | N/A |

| iGPU architecture | GCN radeon r3 |

| iGPU Shader Count | 512 |

| Socket | FM2+ |

AMD: Ryzen

After losing all its market to Intel, AMD introduced the ryzen processor. We will discuss further about these processors in next article let’s keep it a secret now.

Great blog here! Also your site loads up very fast! What web host are you using? Can I get your affiliate link to your host? I wish my website loaded up as fast as yours lol

Glad to know that you liked the information.

Our affiliate Link to buy hosting: https://www.hostg.xyz/aff_c?offer_id=6&aff_id=55753

Buy hosting from our affiliate link and a discount on hosting by applying coupon code: HONEY10